Electronics | Free Full-Text | DuckCore: A Fault-Tolerant Processor Core Architecture Based on the RISC-V ISA

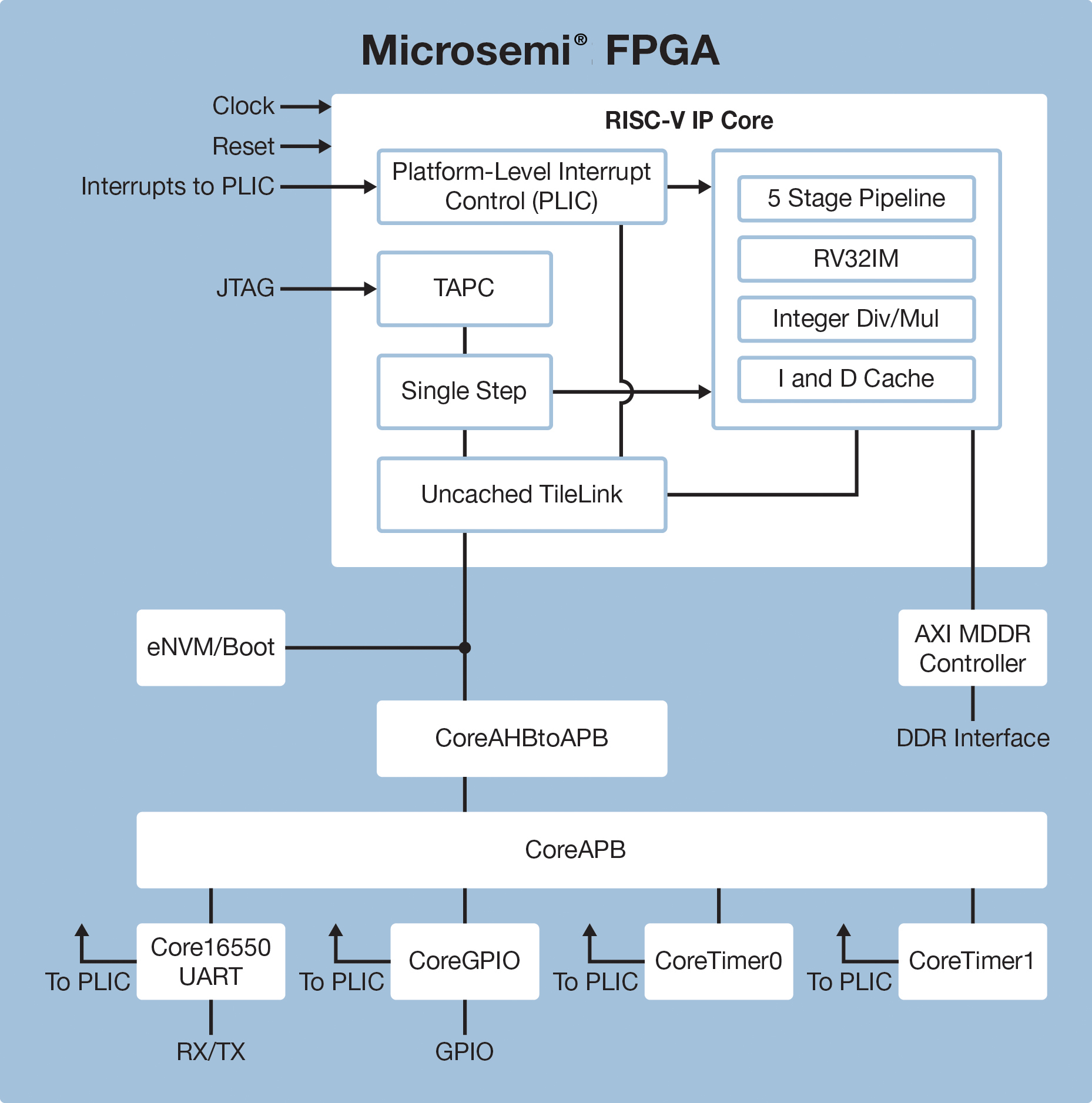

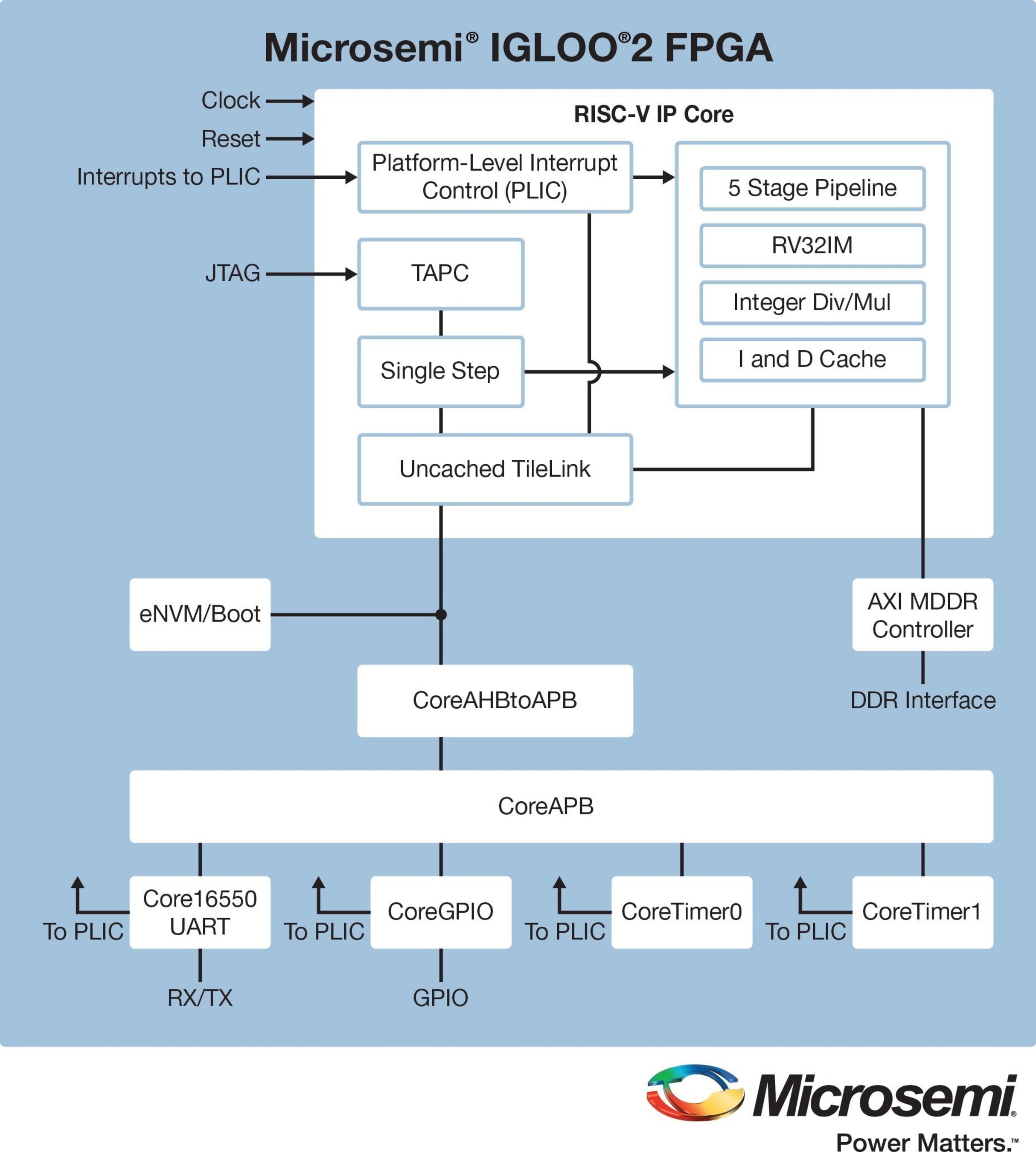

Microsemi is First FPGA Provider to Offer Open Architecture RISC-V IP Core and Comprehensive Software Solution for Embedded Designs

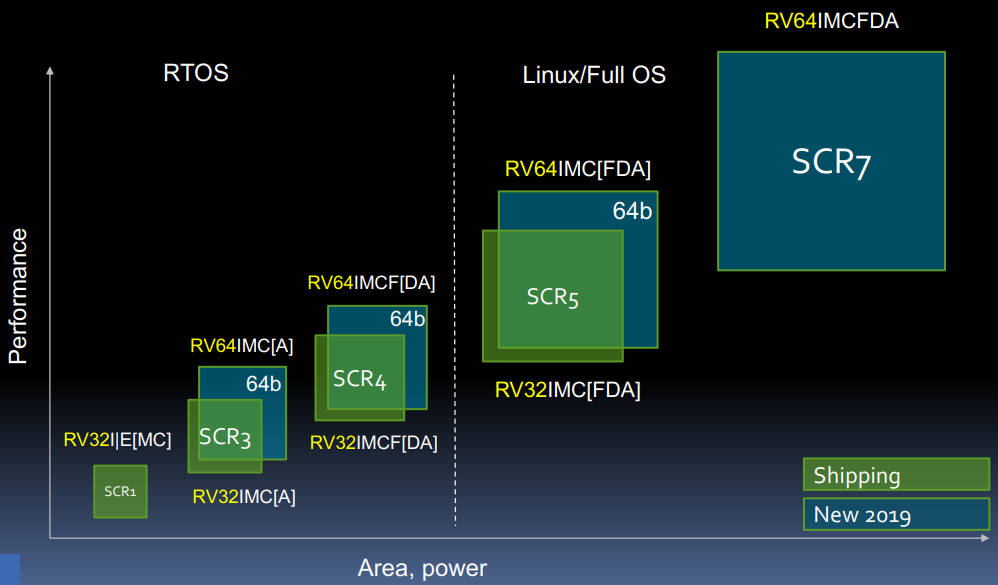

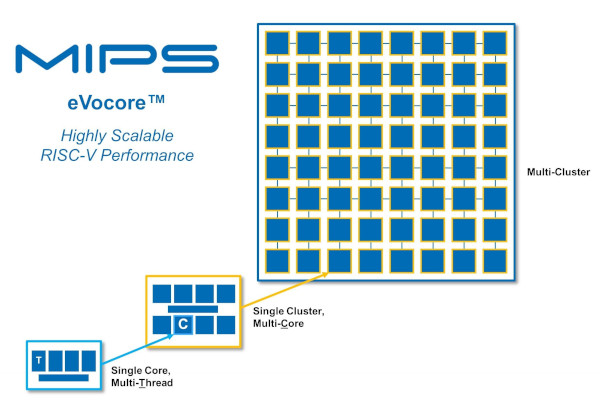

RISC-V alla riscossa: la prima CPU per server, processori fino a 512 core e microcontrollori | Hardware Upgrade

![Just Launched: Computer Architecture with an Industrial RISC-V Core [RVfpga] (LFD119x) - Linux Foundation - Training Just Launched: Computer Architecture with an Industrial RISC-V Core [RVfpga] (LFD119x) - Linux Foundation - Training](https://training.linuxfoundation.org/wp-content/uploads/2023/07/Training_LFD119x_course_1200x628_new.png)